### Script generated by TTT

Title: Petter: Programmiersprachen (19.10.2016)

Date: Wed Oct 19 14:48:05 CEST 2016

Duration: 67:19 min

Pages: 31

# **Need for Concurrency**

Consider two processors:

- in 1997 the Pentium P55C had 4.5M transistors

- in 2006 the Itanium 2 had 1700M transistors

- $\leadsto$  Intel could have built a processor with 256 Pentium cores in 2006

### ⚠ However:

- most programs are not inherently parallel

- → parallelizing a program is between difficult and impossible

- correctly communicating between different cores is challenging

- --- correctness of concurrent communication is very hard

- low-level aspects: locking algorithms must be correct

- high-level aspects: program may deadlock

- a program on n cores runs  $m \ll n$  times faster

- --- all effort is voided if program runs no faster

- distributing work load is application specific

# **Need for Concurrency**

Consider two processors:

- in 1997 the *Pentium P55C* had 4.5M transistors

- in 2006 the Itanium 2 had 1700M transistors

- → Intel could have built a processor with 256 Pentium cores in 2006

Memory Consistency

Motivation

2/3

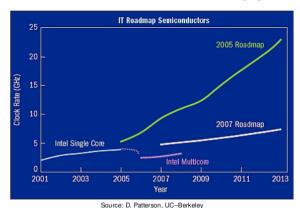

### The free lunch is over

Single processors cannot be made much faster due to physical limitations.

Source: D. Patterson, UC-Berkeley

Memory Consistency Motivation

Memory Consistend

Motivation

### The free lunch is over

Single processors cannot be made much faster due to physical limitations.

But Moore's law still holds for the number of transistors:

- they double every 18 months for the foreseeable future

- may translate into doubling the number of cores

- → programs have to become parallel

Memory Consistency

Motivation

3 / 51

#### \_\_\_

# **Concurrency for the Programmer**

How is concurrency exposed in a programming language?

- spawning of new concurrent computations

- communication between threads

Communication can happen in many ways:

- communication via shared memory (this lecture)

- atomic transactions on shared memory

- message passing

### **Learning Outcomes**

- Happened-before Partial Order

- Sequential Consistency

- The MESI Cache Model

- Weak Consistency

- Memory Barriers

# **Concurrency for the Programmer**

- spawning of new concurrent computations

- communication between threads

Memory Consistency

Motivatio

4/3

### **Communication between Cores**

We consider the concurrent execution of these functions:

#### Thread A

# Thread B

```

void foo(void) {

a = 1;

b = 1;

}

void bar(void) {

while (b == 0) {};

assert(a == 1);

}

```

- initial state of a and b is 0

- A writes a before it writes b

- B should see b go to 1 before executing the assert statement

- the assert statement should always hold

- here the code is correct if the assert holds

- → correctness means: writing a 1 to a happens before reading a 1 in b

#### **Definition (Strict consistency)**

Read operations from location l return values, written by the most recent write operation to l.

Mamany Canaistanay

mory Consistency

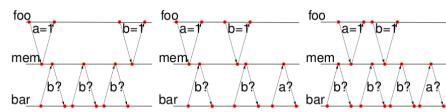

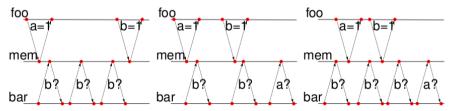

### **Strict Consistency**

Assuming foo and bar are started on two cores operating in lock-step. Then *one* of the following may happen:

Memory Consistency

6/51

### **Strict Consistency**

Assuming foo and bar are started on two cores operating in lock-step. Then *one* of the following may happen:

A unique order between memory accesses is unrealistic in reality:

- each conditional (and loop iteration) doubles the number of possible lock-step executions

- processors use caches → lock-step assumption is violated since cache behavior depends on data

Memory Consistency

lemory Consisten

----

# **Strict Consistency**

Assuming foo and bar are started on two cores operating in lock-step. Then *one* of the following may happen:

A unique order between memory accesses is unrealistic in reality:

- each conditional (and loop iteration) doubles the number of possible lock-step executions

- processors use caches → lock-step assumption is violated since cache behavior depends on data

→ strict consistency is too strong to be realistic ldea: state correctness in terms of what event *may* happen before another one

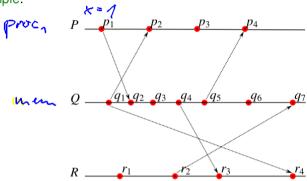

**Events in a Distributed System**

W

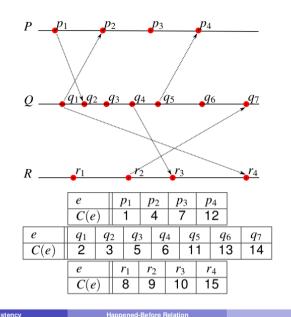

A process as a series of events [Lam78]: Given a distributed system of processes  $P, Q, R, \ldots$ , each process P consists of events  $\bullet p_1, \bullet p_2, \ldots$

Memory Consistency Happened-Before Relation 8

Memory Consistency

Memory Consistency

## **Events in a Distributed System**

A process as a series of events [Lam78]: Given a distributed system of processes  $P, Q, R, \ldots$ , each process P consists of events  $\bullet p_1, \bullet p_2, \ldots$  Example:

- event • $p_i$  in process P happened before • $p_{i+1}$

- if • $p_i$  is an event that sends a message to Q then there is some event • $q_j$  in Q that receives this message and • $p_i$  happened before • $q_j$

Memory Consistence

Happened-Before Relation

8/5

# **The Happened-Before Relation**

#### **Definition**

If an event p happened before an event q then  $p \rightarrow q$ .

memory Consistency

appened-Before Relation

# The Happened-Before Relation

#### **Definition**

If an event p happened before an event q then  $p \rightarrow q$ .

#### Observe:

- $\bullet$   $\rightarrow$  is partial (neither  $p \rightarrow q$  or  $q \rightarrow p$  may hold)

- $\rightarrow$  is irreflexive  $(p \rightarrow p \text{ never holds})$

- $\rightarrow$  is transitive  $(p \rightarrow q \land q \rightarrow r \text{ then } p \rightarrow r)$

- ullet is asymmetric (if  $p \rightarrow q$  then  $\neg (q \rightarrow p)$ )

$\leadsto$  the  $\to$  relation is a *strict partial order*

# **Concurrency in Process Diagrams**

Let  $a \not\rightarrow b$  abbreviate  $\neg (a \rightarrow b)$ .

#### **Definition**

Two distinct events p and q are said to be *concurrent* if  $p \not\rightarrow q$  and  $q \not\rightarrow p$ .

- $p_1 \rightarrow r_4$  in the example

- $p_3$  and  $q_3$  are, in fact, concurrent since  $p_3 \not\rightarrow q_3$  and  $q_3 \not\rightarrow p_3$

Memory Consistency

Hannand Before Beletion

Memory Consistenc

Happened-Before Relation

# **Ordering**

Let C be a *logical clock* that assigns a time-stamp C(p) to each event p.

#### **Definition (Clock Condition)**

Function C satisfies the *clock condition* if for any events p, q

### **Ordering**

Let C be a *logical clock* that assigns a time-stamp C(p) to each event p.

#### **Definition (Clock Condition)**

Function C satisfies the *clock condition* if for any events p, q

$$p \to q \implies C(p) < C(q)$$

For a distributed system the *clock condition* holds iff:

- $\bigcirc$   $p_i$  and  $p_i$  are events of P and  $p_i \rightarrow p_i$  then  $C(p_i) < C(p_i)$

- $\bigcirc$  p is the sending of a message by process P and q is the reception of this message by process Q then C(p) < C(q)

# **Ordering**

Let C be a *logical clock* that assigns a time-stamp C(p) to each event p.

### **Definition (Clock Condition)**

Function C satisfies the *clock condition* if for any events p, q

$$p \rightarrow q \implies C(p) < C(q)$$

For a distributed system the *clock condition* holds iff:

- 2 p is the sending of a message by process P and q is the reception of this message by process Q then C(p) < C(q)

→ a logical clock C that satisfies the clock condition describes a total order a < b (with C(a) < C(b)) that *embeds* the strict partial order  $\rightarrow$

# **Ordering**

Let C be a *logical clock* that assigns a time-stamp C(p) to each event p.

### **Definition (Clock Condition)**

Function C satisfies the *clock condition* if for any events p, q

$$p \to q \implies C(p) < C(q)$$

For a distributed system the *clock condition* holds iff:

- $\bigcirc$  p is the sending of a message by process P and q is the reception of this message by process Q then C(p) < C(q)

→ a logical clock C that satisfies the clock condition describes a total order a < b (with C(a) < C(b)) that *embeds* the strict partial order  $\rightarrow$

The *set* defined by all *C* that satisfy the clock condition is exactly the *set* of executions possible in the system.

$\rightarrow$  use the process model and  $\rightarrow$  to define better consistency model

Given:

Memory Consistency

Happened-Before Relatior

**Defining** C Satisfying the Clock Condition

Given:

# **Summing up Happened-Before Relations**

We can model concurrency using processes and events:

- there is a *happened-before* relation between the events of each process

- there is a *happened-before* relation between communicating events

- happened-before is a strict partial order

- a clock is a total strict order that embeds the happened-before partial order

Sequential Consistency on Multi-Processor Machines

emory Consistency Happened-Before Relation 13/51 Memory Consistency Sequential Consistency 14/51

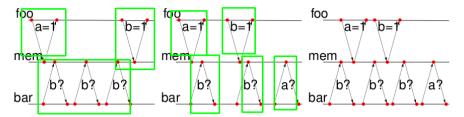

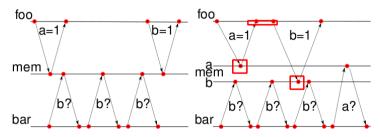

## **Moving Away from Strict Consistency**

Idea: use process diagrams to model more relaxed memory models.

Given a path through each of the threads of a program:

- consider the actions of each thread as events of a process

- use more processes to model memory

- here: one process per variable in memory

# **Moving Away from Strict Consistency**

Idea: use process diagrams to model more relaxed memory models.

Given a path through each of the threads of a program:

- consider the actions of each thread as events of a process

- use more processes to model memory

- here: one process per variable in memory

- concisely represent *some* interleavings

We obtain a model for sequential consistency.

## **Definition: Sequential Consistency**

**Definition (Sequential Consistency Condition [Lam78])**

The result of any execution is the same as if

- the operations of all the processors were executed in some sequential order and

- the operations of each individual processor appear in this sequence in the order specified by its program.

Sequential Consistency applied to Multiprocessor Programs:

Given a program with n threads,

- of for fixed operation sequences  $p_0^1, p_1^1, \ldots$  and  $p_0^2, p_1^2, \ldots$  and  $p_0^n, p_1^n, \ldots$ keeping the program order

- **2** executions obey the clock condition on the  $p_i^i$ ,

- all executions have the same result

Yet, in other words:

- • defines the execution path of each thread

- each execution mentioned in 2 is one *interleaving* of processes

- • declares that the result of running the threads with these interleavings is always the same.

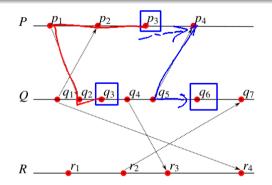

**Disproving Sequential Consistency**

### Sequential Consistency in Multiprocessor Programs:

Given a program with n threads,

- for fixed operation sequences  $p_0^1, p_1^1, \ldots$  and  $p_0^2, p_1^2, \ldots$  and  $p_0^n, p_1^n, \ldots$ keeping the program order

- executions obey the clock condition on the p<sub>i</sub>,

- all executions have the same result

Idea for showing that a system is *not* sequentially consistent:

- pick a result obtained from a program run on a SC system

- pick an execution and a total ordering of all operations ■

- add extra processes to model other system components

- the original order ② becomes a partial order →

- show that total orderings C' exist for  $\rightarrow$  for which the result differs

### **Weakening the Model**

There is no observable change if calculations on different memory locations can happen in parallel.

Idea: model each memory location as a different process

Sequential consistency still obeyed:

- the accesses of foo to a occurs before b

- the first two read accesses to b are in parallel to a=1

**Memory Consistency**

Sequential Consistency

40 / 5

**Memory Consistency**

quential Consistency

19 / 51

# **Benefits of Sequential Consistency**

Benefits of the sequential consistency model:

- concisely represent all interleavings that are due to variations in speed

- synchronization using time is uncommon for software

- → a good model for correct behaviors of concurrent programs

- programs results besides SC results are undesirable (they contain *races*)

It is a realistic model for older hardware:

- sequential consistency model suitable for concurrent processors that acquire exclusive access to memory

- processors can speed up computation by using caches and still maintain sequential consistency

### **Benefits of Sequential Consistency**

Benefits of the sequential consistency model:

- concisely represent all interleavings that are due to variations in speed

- synchronization using time is uncommon for software

- → a good model for correct behaviors of concurrent programs

- → programs results besides SC results are undesirable (they contain races)

13

# Benefits of Sequential Consistency

Benefits of the sequential consistency model:

- concisely represent all interleavings that are due to variations in speed

- synchronization using time is uncommon for software

- → a good Model for correct behaviors of concurrent programs

- → programs results besides SC results are undesirable (they contain races)

It is a realistic model for older hardward:

- sequential consistency model suitable for concurrent processors that acquire exclusive access to memory

- processors can speed up computation by using eaches and still maintain sequential onsistency

Not a realistic model for modern hardware with out-of-order execution:

- what other processors see is determined by complex optimizations to caching

- --- need to understand how caches worth

Manager Consistence

Sequential Consistency

Memory Consistency

Sequential Consistency

19 / 5